Dernière mise à jour à 15h36 le 28/05

Une équipe de recherche de l'Université Fudan a découvert une nouvelle architecture de base pour les puces, qui devrait permettre d'obtenir une efficacité de surface supérieure en divisant par deux l'espace de la porte logique, ou bloc élémentaire d'un circuit numérique.

L'étude, dirigée par les professeurs Zhang Wei et Zhou Peng de la faculté de microélectronique de l'Université Fudan, sera prochainement publiée sur Nature Nanotechnology, une revue universitaire de premier plan consacrée aux nanosciences et aux nanotechnologies.

Selon le professeur Zhang, ce genre de transistor à l'état de prototype est basé sur un matériau bidimensionnel capable de réaliser une logique de photo-permutation dans une cellule unique, grâce à ses canaux à deux surfaces.

Ce transistor va probablement étendre la loi de Moore, selon laquelle le nombre de transistors dans un circuit intégré dense double tous les 18 mois environ. Mais, ces dernières années, cette théorie a été contestée par les industriels qui ont de plus en plus de mal à réduire davantage encore la taille des puces.

La taille réduite des puces qui en résulte va grandement améliorer les performances informatiques et réduire encore les coûts.

« Ces dispositifs ont un potentiel pour devenir des candidats prometteurs pour la construction de nouvelles puces capables d'effectuer des calculs et du stockage avec des fonctions uniques et avec une efficacité de zone élevée », a précisé le professeur Zhou.

« Ces travaux ouvrent de nouveaux horizons à la recherche de solutions prometteuses pour les appareils électroniques et une architecture de circuit innovante ... Le concept d'application exceptionnel pour les circuits intégrés de prochaine génération à semi-conducteurs bidimensionnels ouvrira une nouvelle porte à l'informatique et à la mémoire », a ajouté un communiqué du comité de révision de la revue.

Beijing propose des mesures pour stimuler l'innovation dans l'IA

Beijing propose des mesures pour stimuler l'innovation dans l'IA Les experts recommandent un régime alimentaire plus sain pour réduire les risques

Les experts recommandent un régime alimentaire plus sain pour réduire les risques Ouverture de la Semaine des docteurs de Chongqing 2019 pour attirer les talents

Ouverture de la Semaine des docteurs de Chongqing 2019 pour attirer les talents La Chine accroît sa part de superordinateurs dans le Top 500 mondial

La Chine accroît sa part de superordinateurs dans le Top 500 mondial La Chine annonce une feuille de route pour construire une armée de l'air moderne plus forte

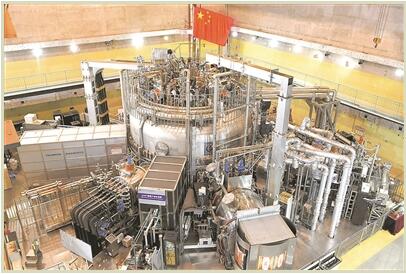

La Chine annonce une feuille de route pour construire une armée de l'air moderne plus forte Le « Soleil artificiel chinois » dépasse les 100 millions de degrés

Le « Soleil artificiel chinois » dépasse les 100 millions de degrés La Chine lance deux satellites BeiDou

La Chine lance deux satellites BeiDou Des chercheurs suivent la dynamique de l'emploi et du logement

Des chercheurs suivent la dynamique de l'emploi et du logement  Ceux qui veulent nous rejoindre sur la messagerie WeChat, scannez le code QR ci-contre.

Ceux qui veulent nous rejoindre sur la messagerie WeChat, scannez le code QR ci-contre. La MTC en quête de normes reconnues dans l'Union européenne

La MTC en quête de normes reconnues dans l'Union européenne Des cartes bancaires plus sûres en vedette au 2e Sommet Chine numérique

Des cartes bancaires plus sûres en vedette au 2e Sommet Chine numérique Les technologies fondamentales visent à offrir un meilleur appui à la numérique

Les technologies fondamentales visent à offrir un meilleur appui à la numérique A Zhuhai, le spectacle est aussi dans les airs !

A Zhuhai, le spectacle est aussi dans les airs !